# NANO LETTERS

2008 Vol. 8, No. 2 706-709

# A 1 GHz Integrated Circuit with Carbon Nanotube Interconnects and Silicon Transistors

Gael F. Close,† Shinichi Yasuda,‡ Bipul Paul, $^{\pounds}$  Shinobu Fujita,‡ and H.-S. Philip Wong\*,†

Department of Electrical Engineering, Stanford University, Stanford, California 94025, Advanced LSI Technology Laboratory, Toshiba Corporation, Kawasaki, Japan, and Toshiba America Research, San Jose, California

Received November 27, 2007; Revised Manuscript Received December 20, 2007

#### **ABSTRACT**

Due to their excellent electrical properties, metallic carbon nanotubes are promising materials for interconnect wires in future integrated circuits. Simulations have shown that the use of metallic carbon nanotube interconnects could yield more energy efficient and faster integrated circuits. The next step is to build an experimental prototype integrated circuit using carbon nanotube interconnects operating at high speed. Here, we report the fabrication of the first stand-alone integrated circuit combining silicon transistors and individual carbon nanotube interconnect wires on the same chip operating above 1 GHz. In addition to setting a milestone by operating above 1 GHz, this prototype is also a tool to investigate carbon nanotubes on a silicon-based platform at high frequencies, paving the way for future multi-GHz nanoelectronics.

The performances of integrated circuits have been steadily improved over the last few decades through miniaturization of the transistors and the interconnect wires. In addition to shrinking the building blocks, new materials have been progressively introduced in the manufacturing of integrated circuits to further improve their performances. Maintaining this trend of higher-performance integrated circuits into the future will increasingly require the use of materials at the nanoscale. Due to their nanoscale size and outstanding intrinsic electronic properties, carbon nanotubes (CNTs) are promising materials for future nanoelectronics. Semiconducting CNTs are already being researched as the electron channel for nanotransistors. 1,2 Similarly, metallic CNTs have also been proposed as effective wires<sup>3-5</sup> for interconnecting the transistors. In this work, we have built the first integrated circuit combining silicon transistors and CNT interconnect wires on the same chip operating above 1 GHz. This prototype demonstrates that a single carbon nanotube can be effectively used to transmit GHz digital signals in between transistors.

The most advanced integrated circuits consist of several millions (sometimes billions) of transistors, interconnected by kilometers of copper wires within a 1 cm<sup>2</sup> silicon chip. The number of transistors integrated on a single chip is

predicted to increase even further,<sup>6</sup> requiring even smaller transistors and narrower copper wires in the future. As copper wires are scaled down, they face two principal issues. First, their electrical resistivity degrades due to increasing electron scattering by the grain boundaries and the wire surface.<sup>7–9</sup> Second, their reliability is becoming a growing concern due to the increasing current density (>2 MA/cm<sup>2</sup>) that they need to withstand. 10 A quest for alternative interconnect materials engineered at the nanoscale has thus been initiated to solve these two problems. 11 Metallic CNTs are attractive interconnect materials because they address, in principle, the two problems faced by copper wires. First, due to their 1-D nature, electrons can travel much further than in copper without scattering. 12,13 Second, they can withstand current density greatly exceeding the limit of copper.<sup>14</sup> Another advantage of metallic CNTs as interconnect materials is that they are scalable all the way down to the 1 nm regime.<sup>5</sup> As a result of these attractive attributes, CNTs are actively researched as future interconnect materials in vertical vias15-17 and horizontal interconnects.18 However, cointegrating CNT interconnects in the dominant silicon-based CMOS platform remains a challenge.

In fact, there has been no experimental demonstration that a metallic CNT can indeed function as an interconnect wire in an electronic chip and successfully transmit GHz digital signals from one transistor to another. Previous attempts<sup>19,20</sup> to co-integrate silicon transistors and CNTs were limited to the low-frequency regime. Others<sup>21–24</sup> have recently mea-

$<sup>\</sup>ast$  To whom correspondence should be addressed. E-mail: hspwong@stanford.edu.

<sup>†</sup> Stanford University.

<sup>&</sup>lt;sup>‡</sup> Toshiba Corporation, Japan.

<sup>&</sup>lt;sup>£</sup> Toshiba America Research.

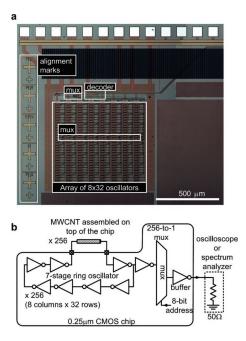

**Figure 1.** CMOS platform chip before the assembly of the MWCNT interconnects. (a) Chip photograph. (b) Circuit diagram. The chip, which is fabricated in a  $0.25 \,\mu \text{m}$  CMOS process, contains 256 ring oscillators with an intentionally missing interconnect wire, to be implemented with a MWCNT. In addition, the chip contains selection circuitry (multiplexer: mux, and decoders).

sured the electrical properties of individual CNT interconnects in the radio frequency regime (>1 GHz), but their functionality as an interconnect wire in a working standalone integrated circuit has not been demonstrated.

We address this need in this letter. We designed, fabricated, and tested the first integrated circuit with silicon-based transistors and CNT interconnects operating above 1 GHz. More specifically, we assembled multi-wall CNT (MWCNT) interconnects on top of a CMOS chip fabricated in a 0.25  $\mu$ m silicon CMOS process containing about 11 000 transistors. The MWCNTs were used as electrical wires interconnecting various stages of conventional ring oscillators. Successful co-integration of silicon transistors and MWCNT interconnects was demonstrated by the correct functionality of the fabricated oscillators.

The CMOS platform chip consisted of an array of 256 ring oscillators and the selection circuitry to select one ring oscillator at a time. The total chip area was 5 mm  $\times$  5 mm, but the circuitry described in this paper only occupied 1/8 of the total area. The chip was fabricated in a 0.25  $\mu$ m CMOS process. Figure 1 shows the CMOS chip photograph and the circuit diagram. By design, each oscillator was missing one interconnect wire and therefore did not oscillate as it was.

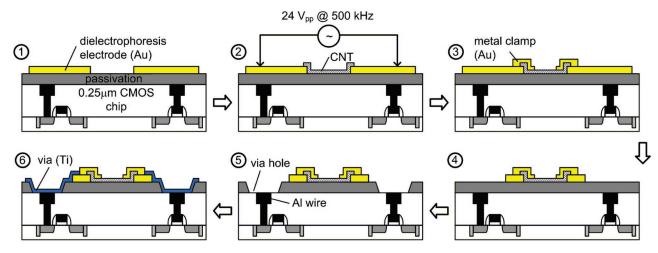

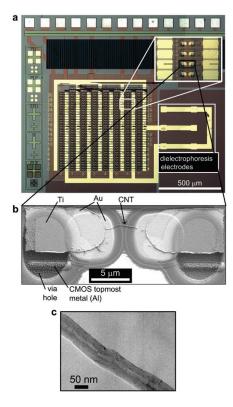

The bare CMOS chip was postprocessed in the clean room of the Stanford Nanofabrication Facility. Growing MWCNTs directly on the CMOS chip was not possible as it would have damaged the CMOS circuitry due to the high temperature required for MWCNT growth (typically >500C). Instead, we used commercially available MWCNTs with an average length around 5  $\mu$ m and an average diameter around 70 nm. The process flow is illustrated in Figure 2. We first patterned an array of gaps in between gold electrodes. We dispersed the MWCNTs in ethanol. We then applied an alternating electric field to assemble and precisely position the MWCNTs in the gaps between the gold electrodes using the dielectrophoretic effect.<sup>23,25,26</sup> The MWCNTs were then secured in place by metal clamps deposited at both ends of the MWCNTs. Once the MWCNTs were on the chip, via holes were etched through the CMOS passivation layer to reveal the topmost aluminum metal layer of the CMOS chip. The vias were finally filled with titanium, thereby establishing electrical connections between the underlying silicon CMOS transistors and the MWCNT interconnects. Figure 3 shows the chip at the end of the MWCNT assembly process. As the MWCNT interconnects were precisely assembled by dielectrophoresis literally right on top of the silicon transistors, the parasitic capacitances were minimized (<10 fF). This is a key aspect of this work because it allows operation above 1 GHz for the first time.

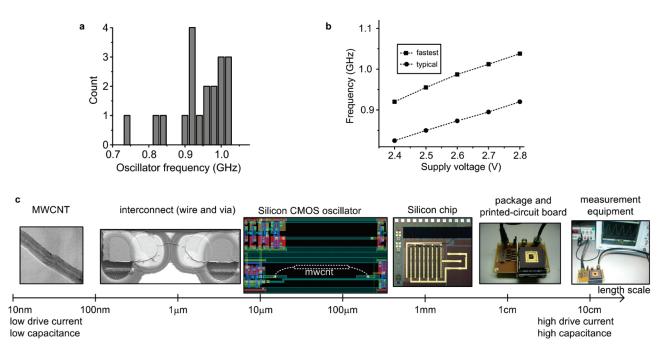

The postprocessed chip was wire bonded to a pin grid array package and mounted onto a printed circuit board for electrical testing. The oscillation amplitude and frequency were measured with a spectrum analyzer. The 19 oscillators out of 256 (yield  $\sim$  8%, limited by the MWCNT dielectrophoresis assembly) that were properly wired by a MWCNT interconnect did indeed oscillate (Figure 4a,b), demonstrating

Figure 2. Process flow to assemble an array of MWCNT interconnects on top of a platform CMOS chip.

Nano Lett., Vol. 8, No. 2, **2008**

**Figure 3.** CMOS platform chip after the assembly of the MWCNT interconnects on the chip surface. (a) Chip photograph. (b) Close-up SEM image of one fabricated MWCNT interconnect on top of the chip. The white cloud surrounding the metals in the SEM image is an artifact due to charging of the sample during SEM imaging. (c) TEM image of a typical MWCNT used in this work.

the feasibility of MWCNT interconnects in a silicon environment. The fastest oscillators oscillated at a frequency above 1 GHz, confirming that MWCNT interconnects can successfully transmit GHz signals. All of the assembled MWCNT interconnects had different diameters (from 50 to 100 nm) and different contact geometries. Both of these factors contributed to variations in the resistances of the MWCNT interconnects, which in turn yielded variations in the oscillator frequencies (Figure 4a). The MWCNT interconnect resistance can be inferred from the measured oscillation frequency as follows. Recalling that the oscillation period of a ring oscillator is given by twice the delay around the oscillator loop, half of the oscillation period equals the sum of two delays, the delay through the CMOS stages plus the RC delay contributed by the MWCNT interconnect resistance and the load capacitance driven by the MWCNT. Modeling the MWCNT interconnect as an ideal resistor, we have used HSpice transistor-level circuit simulations to extract the relationship between the MWCNT resistance  $R_{\text{CNT}}$  and the oscillation period  $T_{\rm osc}$  (see Supporting Information)

$$\frac{T_{\text{osc}}}{2} = 475 \text{ ps} + R_{\text{CNT}} \cdot 5 \text{ fF}$$

Using this equation, we calculated that, for the fastest oscillator operating at 1.02 GHz ( $T_{\rm osc}=980$  ps), the MWCNT interconnect resistance was around 3 k $\Omega$ , consistent with our previous experiments with these MWCNTs.<sup>23</sup> This amounted to a resistivity around 500  $\mu\Omega$ -cm, 2 orders

**Figure 4.** Electrical measurements of the ring oscillators with MWCNT interconnects. (a) Measured oscillation frequency for 19 ring oscillators with MWCNT interconnects at a 2.8 V supply voltage. The oscillators exhibit different oscillation frequencies due to the variability in the assembled MWCNT resistances. The fastest oscillators with MWCNT interconnects operate above 1 GHz at the 2.8 V supply voltage. (b) Measured oscillation frequency as a function of the supply voltage for two particular oscillators, the fastest one (with the lowest MWCNT resistance) and a typical one. (c) Test setup across all of the length scales from the nanoscale MWCNT all the way to the macroscopic measurement equipment. This chain of fast intermediate circuits is the key to achieve GHz operation.

708 Nano Lett., Vol. 8, No. 2, 2008

Table 1. Features of the Fabricated Hybrid Integrated Circuit

| Silicon CMOS Chip     |                                  |  |

|-----------------------|----------------------------------|--|

| technology            | $0.25\mu\mathrm{m}$ CMOS         |  |

| supply voltage        | 2.5 - 2.8  V                     |  |

| number of oscillators | 256                              |  |

| number of transistors | 11 000                           |  |

| area                  | $2.5~\text{mm}\times1~\text{mm}$ |  |

## Post-CMOS Assembly of the Carbon Nanotube Interconnects

| number of extra lithography steps         | 4                                |

|-------------------------------------------|----------------------------------|

| carbon nanotube                           |                                  |

| type                                      | multi-wall                       |

| outer diameter                            | ${\sim}50{-}100~\text{nm}$       |

| inner diameter                            | ${\sim}10{-}20~\text{nm}$        |

| length                                    | $\sim$ 5 $\mu\mathrm{m}$         |

| resistivity                               | ${\sim}500~\mu\Omega$ -cm        |

| voltage applied to assemble the nanotubes | $24 V_{\rm pp}$ @ $500 { m kHz}$ |

| nanotube contact metal                    | gold                             |

| via-filling metal                         | titanium                         |

|                                           |                                  |

### Completed Silicon-CMOS/carbon Nanotube Hybrid

| number of working oscillators | 19                  |

|-------------------------------|---------------------|

| highest oscillation frequency | $1.02~\mathrm{GHz}$ |

of magnitude higher than the resistivity of copper. This high resistivity can be attributed to the average structural quality and purity (starting material purity: 95%) of our MWCNT materials rather than to a fundamental limitation of MWCNTs. Work is currently underway to improve the resistivity of our MWCNT interconnects and bring it closer to the resistivity of copper. Higher operation frequencies (>1 GHz) could be achieved by using MWCNTs with lower resistivity or faster silicon CMOS circuits or any combination of the two.

In conclusion, we have demonstrated that CNT interconnects can be integrated with silicon CMOS transistors on the same chip. We have also showed, for the first time, that these CNT interconnects can transmit GHz digital signals between transistors. Table 1 summarizes the features of our prototype integrated circuit. The key in achieving GHz operation with individual MWCNT interconnects, and more generally any individual nanoelectronic devices/structures, is to have a chain of fast circuits spanning all length scales from the nanoscale all the way up to the macroscopic test instruments (Figure 4c). Conventional microelectronic circuits in silicon CMOS technology are natural choices in the middle of this chain because they bridge the gap from the microscale to the macroscopic scale. Without this intermediate CMOS link, individual nanoscale devices would not be able to effectively drive any macroscopic circuits at GHz frequencies directly because of their low current drive compared to the macroscopic parasitic capacitances. Our approach opens up the possibility of in situ GHz benchmarking of nanoelectronic devices in a silicon environment.

**Acknowledgment.** We thank Dr. Ann Marshall for taking the TEM images. This work was partially supported by the Focus Research Program Interconnect Focus Center (IFC) and the Intel Graduate Fellowship for G.C. Work was performed, in part, at the Stanford Nanofabrication Facility

(a member of the National Nanotechnology Infrastructure Network), which is supported by the National Science Foundation under Grant ECS-9731293, its lab members, and the industrial members of the Stanford Center for Integrated Systems. We also thank TSMC for the CMOS chip fabrication.

**Supporting Information Available:** Description of materials and methods including MWCNT suspension and deposition, details of the post-CMOS processing steps, electrical test setup, and a figure showing how to extract the relationship between the oscillation frequency and the MWCNT resistance from HSpice circuit simulation. This material is available free of charge via the Internet at http://pubs.acs.org.

#### References

- Chen, Z.; Appenzeller, J.; Lin, Y.; Sippel-Oakley, J.; Rinzler, A.; Tang, J.; Wind, S.; Solomon, P.; Avouris, P. Science 2006, 311, 1735.

- Avouris, P.; Chen, Z.; Perebeinos, V. Nat. Nanotechnol. 2007, 2, 605.

- (3) Tans, S. J.; Devoret, M. H.; Dai, H. J.; Thess, A.; Smalley, R. E.; Geerligs, L. J.; Dekker, C. Nature 1997, 386, 474.

- (4) White, C. T.; Todorov, T. N. Nature 1998, 393, 240.

- (5) Kong, J.; Yenilmez, E.; Tombler, T.; Kim, W.; Dai, H.; Laughlin, R.; Liu, L.; Jayanthi, C.; Wu, S. Phys. Rev. Lett. 2001, 87, 106801.

- (6) International Technology Roadmap for Semiconductors 2005. http:// www.itrs.net.

- (7) Rossnagel, S. M.; Kuan, T. S. J. Vac. Sci. Technol., B 2004, 22, 240.

- (8) Steinhogl, W.; Schindler, G.; Steinlesberger, G.; Traving, M.; Engelhardt, M. J. Appl. Phys. 2005, 97, 023706.

- (9) Alers, C.; Sukamto, J.; Park, S.; Harm, C.; Reid, J. Semicond. Int. 2006, 29, 38.

- (10) Hau-Riege, C. Microelectron. Reliab. 2004, 44, 195.

- (11) Kaloyeros, A. E.; Eisenbraun, E. T.; Welch, J.; Geer, R. E. Semicond. Int. 2003, 26, 56.

- (12) Li, H. J.; Lu, W. G.; Li, J. J.; Bai, X. D.; Gu, C. Z. Phys. Rev. Lett. 2005, 95, 086601.

- (13) Moon, S.; Song, W.; Kim, N.; Lee, J.; Na, P.; Lee, S.; Park, J.; Jung, M.; Lee, H.; Kang, K.; Lee, C.; Kim, J. Nanotechnology 2007, 18, 235201.

- (14) Wei, B. Q.; Vajtai, R.; Ajayan, P. M. Appl. Phys. Lett. 2001, 79, 1172

- (15) Li, J.; Ye, Q.; Cassell, A.; Ng, H. T.; Stevens, R.; Han, J.; Meyyappan, M. Appl. Phys. Lett. 2003, 82, 2491.

- (16) Awano, Y.; Sato, S.; Kondo, D.; Ohfuti, M.; Kawabata, A.; Nihei, M.; Yokoyama, N. Phys. Status Solidi A 2006, 203, 3611.

- (17) Nihei, M.; Hyakushima, T.; Sato, S.; Nozue, T.; Norimatsu, M.; Mishima, M.; Murakami, T.; Kondo, D.; Kawabata, A.; Ohfuti, M.; Awano, Y. Proc. IEEE Int. Interconnect Technol. Conf. 2007, 204.

- (18) Naeemi, A.; Meindl, J. IEEE Electron Dev. Lett. 2007, 54, 26.

- (19) Tseng, Y.-C.; Xuan, P.; Javey, A.; Malloy, R.; Wang, Q.; Bokor, J.; Dai, H. Nano Lett. 2004, 4, 123.

- (20) Narayanan, A.; Dan, Y.; Deshpande, V.; Lello, N. D.; Evoy, S.; Raman, S. *IEEE Trans. Nanotechnol.* **2006**, *5*, 101.

- (21) Rice, P.; Wallis, T. M.; Russek, S. E.; Kabos, P. Nano Lett. **2007**, 7, 1086.

- (22) Jun, S. C.; Choi, J. H.; Cha, S. N.; Baik, C. W.; Lee, S. C. W.; Kim, H. J.; Hone, J.; Kim, J. M. Nanotechnology 2007, 18, 255701.

- (23) Close, G. F.; Wong, H.-S. P. Proc. IEEE Int. Electron Devices Meet. 2007, 203.

- (24) Plombon, J.; O'Brien, K. P.; Gstrein, F.; Dubin, V. M.; Jiao, Y. Appl. Phys. Lett. 2007, 90, 063106.

- (25) Chung, J. Y.; Lee, K. H.; Lee, J. H.; Ruoff, R. S. Langmuir 2004, 20, 3011.

- (26) Vijayaraghavan, A.; Blatt, S.; Weissenberger, D.; Oron-Carl, M.; Hennrich, F.; Gerthsen, D.; Hahn, H.; Krupke, R. Nano Lett. 2007, 7, 1556.

NL0730965

Nano Lett., Vol. 8, No. 2, **2008**